聚焦三维堆叠技术平台3DLink™,武汉新芯亮相2020重庆ICCAD

2020年12月10-11日,中国集成电路设计业2020年会暨重庆集成电路产业创新发展高峰论坛(以下简称“ICCAD 2020”)在重庆举办。武汉新芯携三维堆叠技术平台3DLink™亮相ICCAD 2020,向观众展示基于该平台打造的多片晶圆堆叠技术及其工艺结构3D模型,并同期展出武汉新芯NOR Flash、电源管理和模拟射频工艺平台。

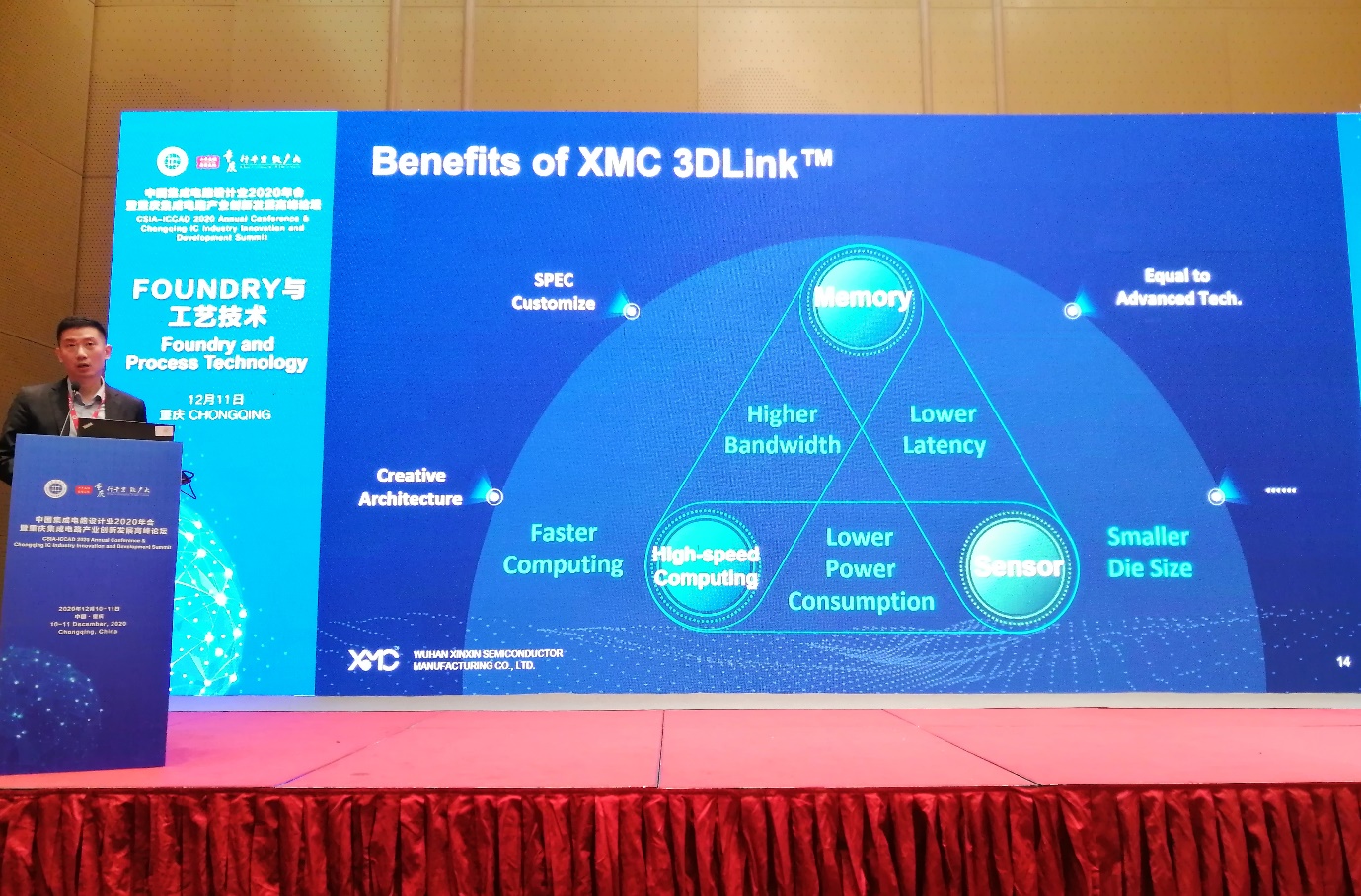

在“Foundry与工艺技术”专题论坛上,武汉新芯代工业务处高级总监沈亮先生发表了题为《XMC 3DLink™——面向存算芯片的解决方案》的精彩演讲,通过介绍数个成功运用3DLink™技术实现创新架构的芯片系统实例,阐述了武汉新芯3DLink™技术对芯片提升带宽、缩小面积等方面带来的划时代推动,激发更多芯片设计的创新思路,赢得了与会嘉宾和观众的一致好评。

首先沈亮重温了武汉新芯过去3年间在ICCAD年会上的技术发布历程,凸显出公司一直在深入地研发3D IC技术,并且会一如既往地借助ICCAD这个平台推广该技术。紧接着沈亮从晶圆级堆叠这个角度揭晓武汉新芯在3D IC领域的技术布局,“3DLink™是公司推出的三维堆叠技术品牌,该技术平台包括目前已研发成功的晶圆间三维堆叠技术,如两片晶圆堆叠和多片晶圆堆叠。”

随后,沈亮立足于客户痛点,结合3DLink™典型市场应用,深入剖析了如何通过武汉新芯三维堆叠技术为客户提供创新的解决方案。“对于存算应用,例如存内计算,它们对带宽和算力有很高的要求,如果采用先进制程工艺来实现理想的性能,成本高而且还需要保证供应的稳定性。”沈亮说道,“武汉新芯的两片晶圆堆叠技术利用晶圆间的Cu-Cu互连,可以实现两片不同工艺的晶圆直接互连,达到更高的互连密度及对准精度。在保证高带宽、强算力、低功耗等性能的情况下,两片晶圆堆叠技术为灵活选择成熟工艺制程来替代先进制程创造了可能。”

3D IC技术不仅是算力芯片的引擎,更颠覆了传统的冯·诺依曼结构,为高带宽存储器芯片提供创新的工艺和架构。沈亮通过3D DRAM和晶圆级HBM的应用案例阐述了三维堆叠技术3DLink™如何有效突破“存储墙”的限制,打造真正的存算一体。“武汉新芯两片晶圆堆叠技术可直接将Memory和Logic晶圆堆叠在一起,并行高效处理架构,在不同功能的晶圆之间实现数据快速传输。”对于晶圆级HBM,沈亮讲道,“多片晶圆堆叠技术打破传统封装级HBM Micro-bump互连架构,采用无凸点(Bumpless)工艺来实现多晶圆直接键合,并利用混合键合工艺实现高密度互连。该技术可以有效克服传统HBM工艺散热性不佳、机械应力不均、工艺繁复、生产效率低下等诸多缺点,在提升产品性能的同时还能大幅提高生产效率。”

在3D传感器方面,沈亮以ToF(Time-of-Flight)为例,指出两片晶圆堆叠技术可满足ToF对大量数据的实时处理需求,通过将感光芯片和逻辑电路上下堆叠起来,兼顾了手机对低功耗和芯片小尺寸的需求。在生动呈现两片晶圆堆叠和多片晶圆堆叠技术在以上典型应用中的方案后,沈亮总结了武汉新芯三维堆叠技术平台的显著优势:创新的架构,更小的芯片尺寸,更高的带宽,更低的功耗和延时。

最后沈亮向与会嘉宾分享了武汉新芯的最新发展情况,包括未来业务聚焦和产能规划,以及3DLink™技术研发布局和生态环境,“公司从2012年便开始布局3D IC技术,到现在已有8年多的研发量产经验,键合良率高达99.5%,拥有超过400个创新专利。目前两片晶圆堆叠技术已量产,多片晶圆堆叠技术已完成工艺研发,未来公司也将积极拓展三维异质集成技术。”武汉新芯3DLink™技术平台具备成熟的设计套件,支持定制化的开发,沈亮向在场的半导体设计业界同行表达了诚挚的合作意愿,“我们已经在3DLink™平台开发并量产创新架构产品,并搭建起更成熟的2.0生态圈,包含更成熟的开发套件、面向应用的差异化工艺解决方案、多种定制存储器支持方案,希望能与更多客户合作,提供高附加值的技术解决方案,共同打造创新集成电路产品。”